Advanced Operating Systems

MS degree in Computer Engineering

University of Rome Tor Vergata

Lecturer: Francesco Quaglia

## Kernel level memory management

- 1. The very base on boot vs memory management

- 2. Memory 'Nodes' (UMA vs NUMA)

- 3. x86 paging support

- 4. Boot and steady state behavior of the memory management system in the Linux kernel

#### **Basic terminology**

- firmware: a program coded on a ROM device, which can be executed when powering a processor on

- **bootsector**: predefined device (e.g. disk) sector keeping executable code for system startup

- bootloader: the actual executable code loaded and launched right before giving control to the target operating system

- ➤ this code is partially kept within the bootsector, and partially kept into other sectors

- It can be used to parameterize the actual operating system boot

#### **Startup tasks**

- The firmware gets executed, which loads in memory and launches the bootsector content

- The loaded bootsector code gets launched, which may load other bootloader portions

- The bootloader ultimately loads the actual operating system kernel and gives it control

- The kernel performs its own startup actions, which may entail architecture setup, data structures and software setup, and process activations

- To emulate a steady state unique scenario, at least one process is derived from the boot thread (namely the IDLE PROCESS)

#### Where is memory management there?

- All the previously listed steps lead to change the image of data that we have in memory

- These changes need to happen just based on various memory handling policies/mechanisms, operating at:

- Kernel load time

- Kernel initialization (including kernel level memory management initialization)

- ✓ Kernel common operations (which make large usage of kernel level memory management services that have been setup along the boot phase)

An initially loaded kernel memory-image is not the same as the one that common applications ``see'' when they are activated

#### Traditional firmware on x86

- It is called BIOS (Basic I/O System)

- Interactive mode can be activated via proper interrupts (e.g. the F1 key)

- Interactive mode can be used to parameterize firmware execution (the parameterization is typically kept via CMOS rewritable memory devices powered by apposite temporary power suppliers)

- The BIOS parameterization can determine the order for searching the boot sector on different devices

- A device boot sector will be searched for only if the device is registered in the BIOS list

#### **Bios bootsector**

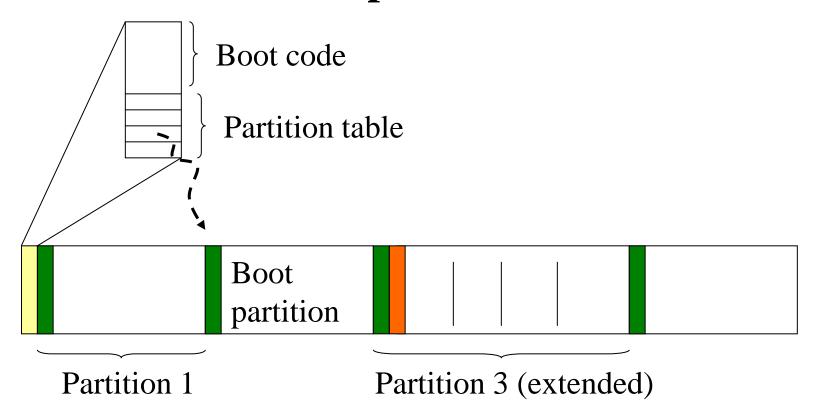

- The first device sector keeps the so called <u>master boot</u> record (MBR)

- This sector keeps executable code and a <u>4-entry tables</u>, each one identifying a different device partition (in terms of its positioning on the device)

- The first sector in each partition can operate as the partition boot sector (BS)

- In case the partition is extended, then it can additionally keep up to 4 sub-partitions (hence the partition boot sector can be structured to keep an additional partitioning table)

- Each sub-partition can keep its own boot sector

## RAM image of the MBR

| Offset | Size (bytes)                            | Description                                     |

|--------|-----------------------------------------|-------------------------------------------------|

| 0      | 436 (to 446, if you need a little extra | MBR Bootstrap (flat binary executable code)     |

| 0x1b4  | 10                                      | Optional "unique" disk ID1                      |

| 0x1be  | 64                                      | MBR Partition Table, with 4 entries (below)     |

| 0x1be  | 16                                      | First partition table entry                     |

| 0x1ce  | 16                                      | Second partition table entry                    |

| 0x1de  | 16                                      | Third partition table entry                     |

| 0x1ee  | 16                                      | Fourth partition table entry                    |

| 0x1fe  | 2                                       | (0x55, 0xAA) "Valid bootsector" signature bytes |

Grub (if you use it) or others

#### An example scheme with Bios

- Boot sector

- Extended partition boot record

Nowadays huge limitation: the maximum size of manageable disks is 2TB

#### **UEFI – Unified Extended Firmware Interface**

- It is the new standard for basic system support (e.g. boot management)

- It removes several limitations of Bios:

- We can (theoretically) handle disks up to 9 zettabytes

- It has a more advanced visual interface

- It is able to run EFI executables, rather than simply running the MBR code

- It offers interfaces to the OS for being configured (rather than being exclusively configurable by triggering its interface with Fn keys at machine startup)

### **UEFI** device partitioning

- Based on GPT (GUID Partition Table)

- GUID = Globally Unique Identifier ..... Theoretically all over the world (if the GPT has in its turn a unique identifier)

- Theoretically unbounded number of partitions kept in this table No longer we need extended partitions for enlarging the partitions' set

- GPT are replicated so that if a copy is corrupted then another one will work this breaks the single point of failure represented by MBR and its partition table

## Bios/UEFI tasks upon booting the OS kernel

- The bootloader/EFI-loader, e.g., GRUB loads in memory the initial image of the operating system kernel

- This includes a ``machine setup code'' that needs to run before the actual kernel code takes control

- This happens since a kernel configuration needs given setup in the hardware upon being launched

- The machine setup code ultimately passes control to the initial kernel image

- In Linux, this kernel image executes starting from the start kernel() in the init/main.c

- This kernel image is way different, both in size and structure, from the one that will operate at steady state

- Just to name one reason, boot is typically highly configurable!

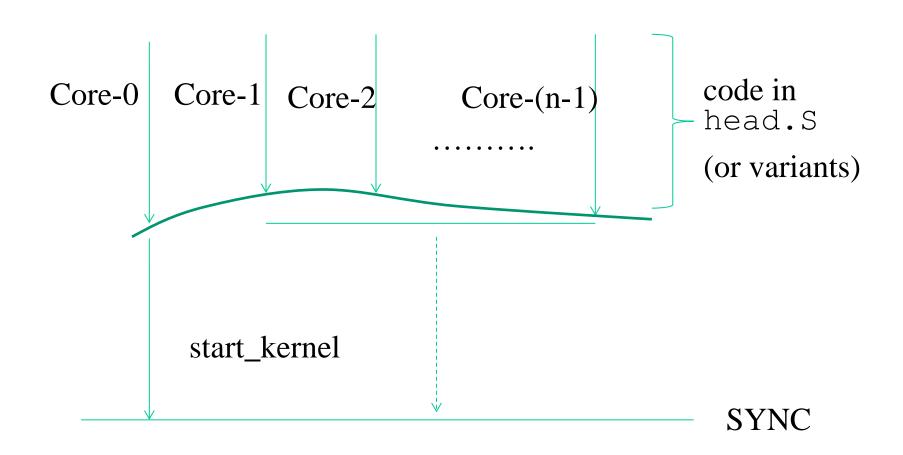

#### What about boot on multi-core machines

- The start\_kernel() function is executed along a single CPU-core (the master)

- All the other cores (the slaves) only keep waiting that the master has finished

- The kernel internal function smp\_processor\_id() can be used for retrieving the ID of the current core

- This function is based on ASM instructions implementing a hardware specific ID detection protocol

- This function operates correctly either at kernel boot or at steady state

# The actual support for CPU-core identification

### x86 Instruction Set Reference

### **CPUID**

#### **CPU Identification**

|   | Opcode | Mnemonic | Description                                                                                                                    |  |

|---|--------|----------|--------------------------------------------------------------------------------------------------------------------------------|--|

| 6 | F A2   | CPUID    | Returns processor identification and feature information to the EAX, EBX, ECX, and EDX registers, according to the input value |  |

|   |        |          | entered initially in the EAX register.                                                                                         |  |

### Actual kernel startup scheme in Linux

# An example head. S code snippet: triggering Linux paging (IA32 case)

```

/* * Enable paging */ 3:

movl $swapper_pg_dir-__PAGE_OFFSET,%eax

movl %eax,%cr3 /* set the page table

pointer.. */

movl %cr0,%eax

orl $0x80000000,%eax

movl %eax,%cr0 /* ..and set paging (PG) bit

*/

```

## Hints on the signature of the start kernel function (as well as others)

..... \_\_init start\_kernel(void)

This only lives in memory during kernel boot (or startup)

The reason for this is to recover main memory storage which is relevant because of both:

- Reduced available RAM (older configurations)

- Increasingly complex (and hence large in size) startup code

Recall that the kernel image is not subject to swap out (conventional kernels are always resident in RAM)

## Management of \_\_init functions

- The kernel linking stage locates these functions on specific logical pages (recall what we told about the fixed positioning of specific kernel level stuff in the kernel layout!!)

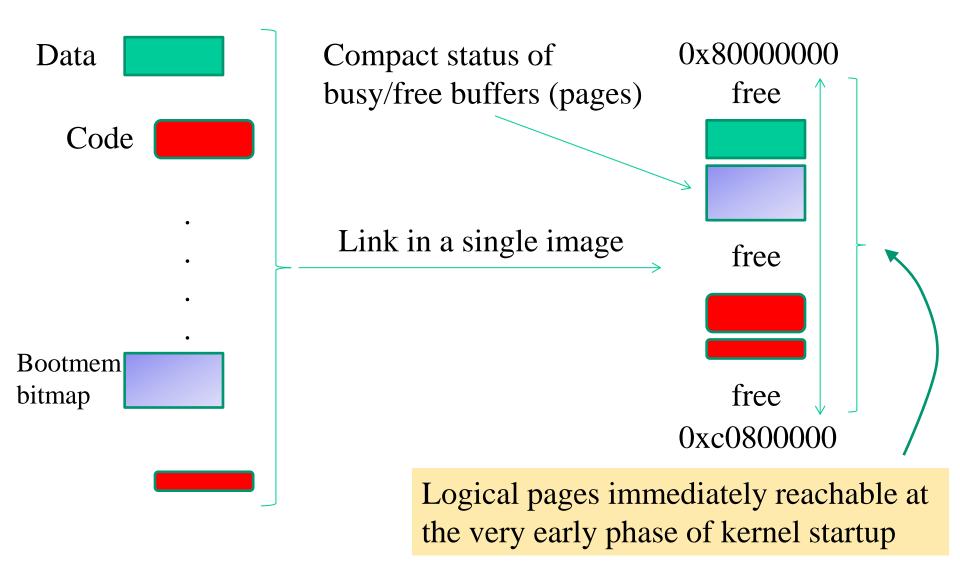

- These logical pages are identified within a "bootmem" subsystem that is used for managing memory when the kernel is not yet at steady state of its memory management operations

- Essentially the bootmem subsystem keeps a bitmask with one bit indicating whether a given page has been used (at compile time) for specific stuff

#### ... still on bootmem

- The bootmem subsystem also allows for memory allocation upon the very initial phase of the kernel startup

- In fact, the data structures (e.g. the bitmaps) it keeps not only indicate if some page has been used for specific data/code

- They also indicate if some page which is actually reachable at the very early phase of boot is not used for any stuff

- These are clearly "free buffers" exploitable upon the very early phase of boot

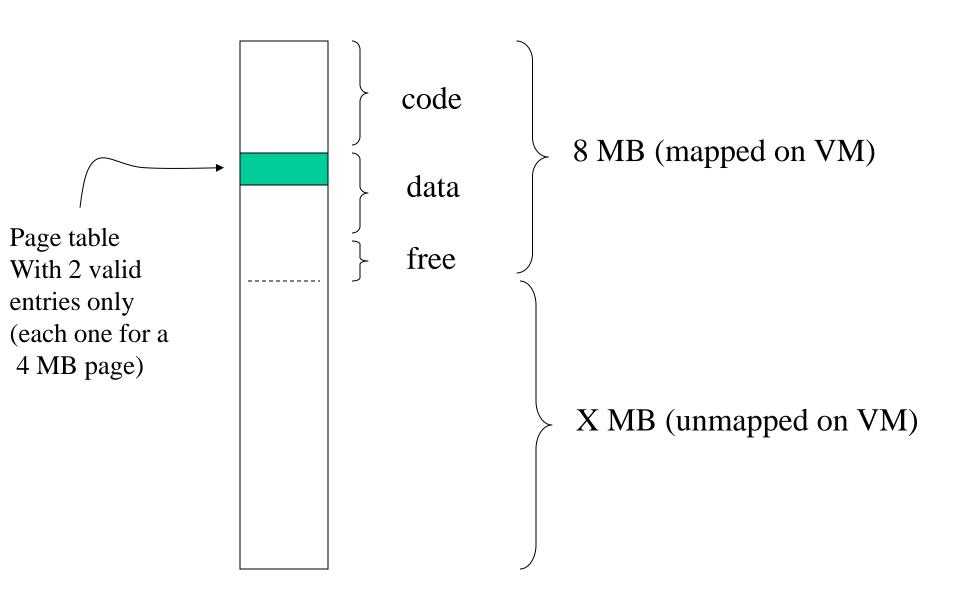

## An exemplified picture of bootmem

## The meaning of "reachable page"

- The kernel software can access the actual content of the page (in RAM) by simply expressing an address falling into that page

- The point is that the expressed address is typically a virtual one (since kernel code is commonly written using `pointer' abstractions)

- So the only way we have to make a virtual address correspond to a given page frame in RAM is to rely on at least a page table that makes the translation (even at the very early stage of kernel boot)

- The initial kernel image has a page table, with a minimum number of pages mapped in RAM, those handled by the bootmem subsystem

# How is RAM memory organized on modern (large scale/parallel) machines?

- In modern chipsets, the CPU-core count continuously increases

- However, it is increasingly difficult to build architectures with a flat-latency memory access (historically referred to as UMA)

- Current machines are typically NUMA

- Each CPU-core has some RAM banks that are close and other that are far

- Generally speaking, each memory bank is associated with a so called NUMA-node

- Modern operating systems are designed to handle NUMA machines (hence UMA as a special case)

# Looking at the Linux NUMA setup via Operating System facilities

- A very simple way is the numactl command

- It allows to discover

- ✓ How many NUMA nodes are present

- ✓ What are the nodes close/far to/from any CPU-core

- ✓ What is the actual distance of the nodes (from the CPU-cores)

Let's see a few 'live' examples ......

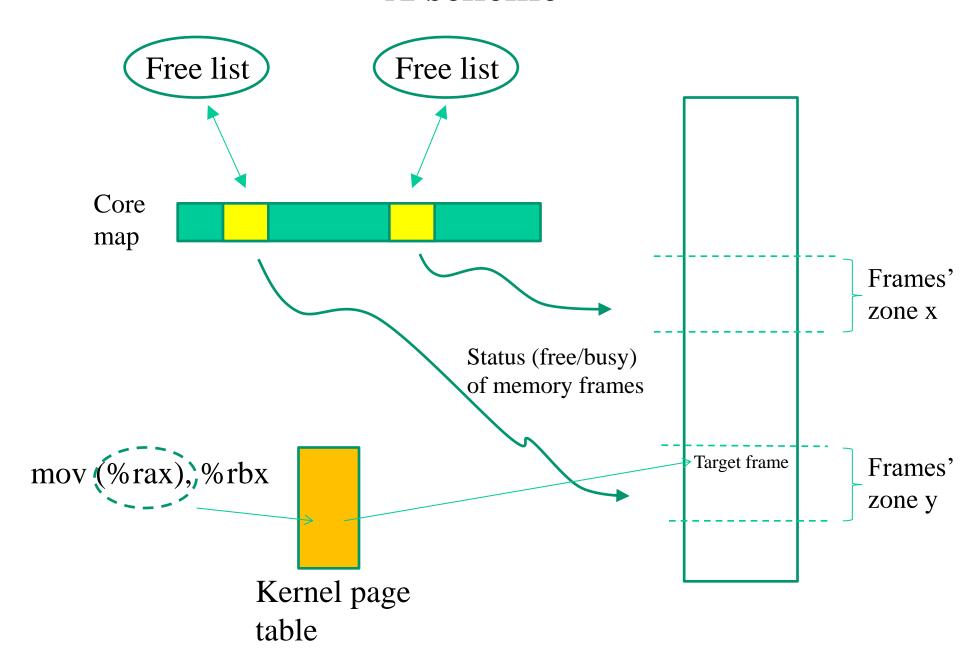

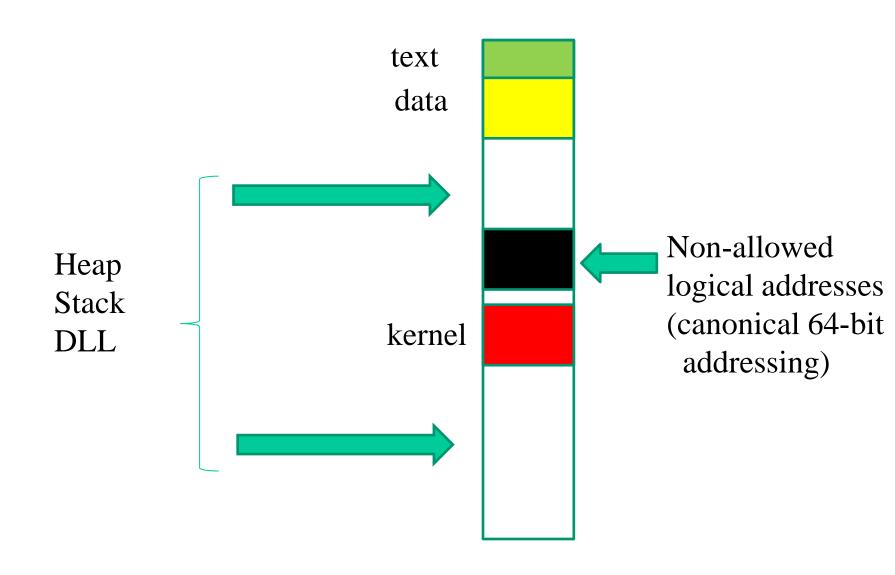

## Actual kernel data structures for managing memory

- Kernel Page table

- This is a kind of 'ancestral' page table (all the others are somehow derived from this one)

- ➤It keeps the memory mapping for kernel level code and data (thread stack included)

- Core map

- The map that keeps status information for any frame (page) of physical memory, and for any NUMA node

- Free list of physical memory frames, for any NUMA node

None of them is already finalized when we startup the kernel

#### A scheme

## Objectives of the kernel page table setup

- These are basically two:

- ✓ Allowing the kernel software to use virtual addressed while executing (either at startup or at steady state)

- ✓ Allowing the kernel software (and consequently the application software) to reach (in read and/or write mode) the maximum admissible (for the specific machine) or available RAM storage

- The finalized shape of the kernel page table is therefore typically not setup into the original image of the kernel loaded in memory, e.g., given that the available RAM to drive can be parameterized

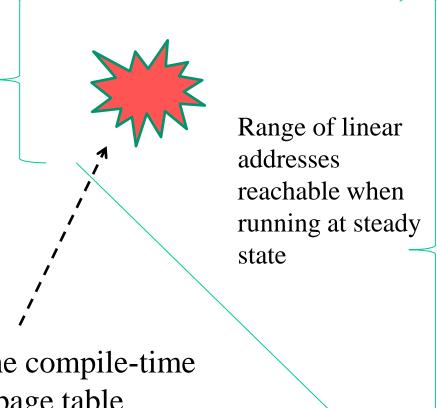

#### A scheme

Range of linear addresses reachable when switching to protected mode plus paging

Increase of the size of reachable RAM locations

Passage from the compile-time defined kernel-page table to the boot time reshuffled one

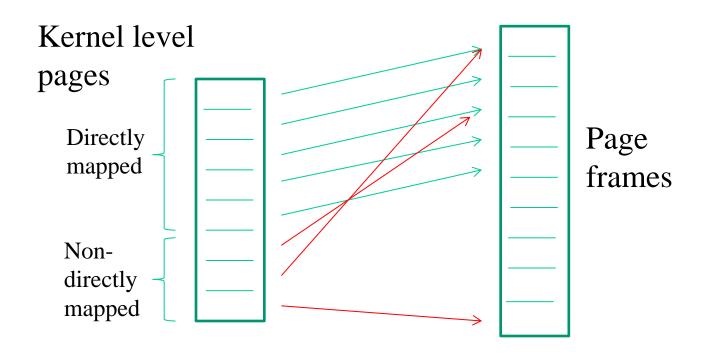

#### Directly mapped memory pages

- They are kernel level pages whose mapping onto physical memory (frames) is based on a simple shift between virtual and physical address

- $\checkmark$  PA = ψ(VA) where ψ is (typically) a simple function subtracting a predetermined constant value to VA

- Not all the kernel level virtual pages are directly mapped

#### Virtual memory vs boot sequence (IA32 example)

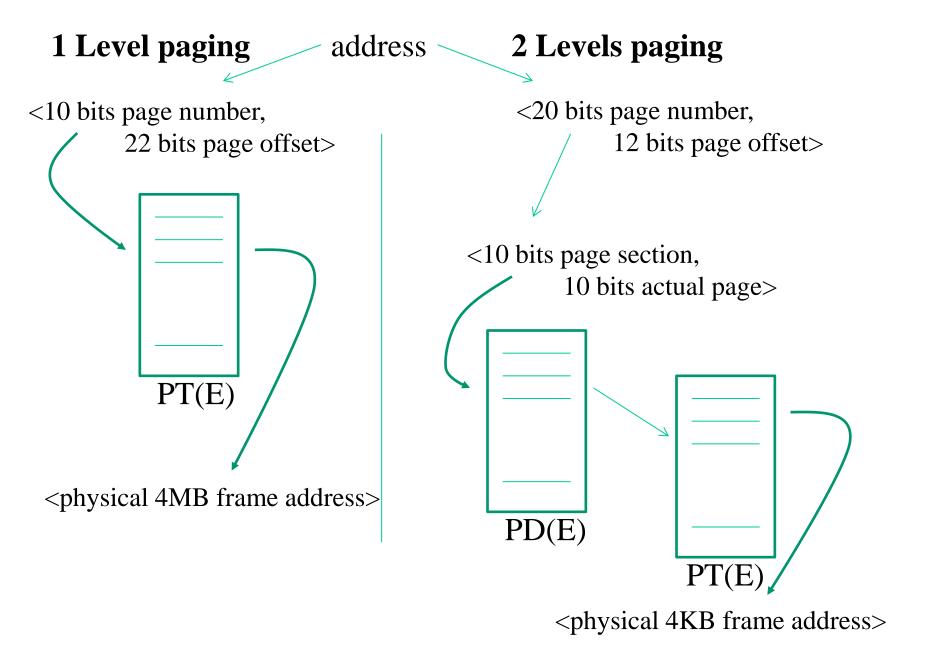

- Upon kernel startup addressing relies on a simple single level paging mechanism that only maps 2 pages (each of 4 MB) up to 8 MB physical addresses

- The actual paging rule (namely the page granularity and the number of paging levels up to 2 in i386) is identified via proper bits within the entries of the page table

- The physical address of the setup page table is kept within the CR3 register

- The steady state paging scheme used by LINUX will be activated during the kernel boot procedure

- The max size of the address space for LINUX processes on i386 machines (or protected mode) is 4 GB

- > 3 GB are within user level segments

- > 1 GB is within kernel level segments

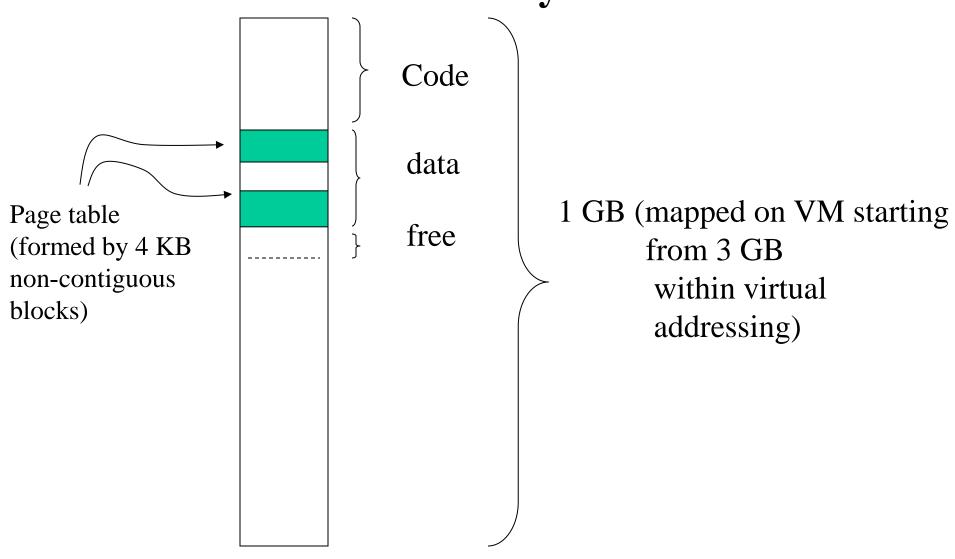

### Details on the page table structure in i386 (i)

#### Details on the page table structure in i386 (ii)

- It is allocated in physical memory into 4KB blocks, which can be non-contiguous

- In typical LINUX configurations, once set-up it maps 4 GB addresses, of which 3 GB at null reference and (almost) 1 GB onto actual physical memory

- Such a mapped 1 GB corresponds to kernel level virtual addressing and allows the kernel to span over 1 GB of physical addresses

- To drive more physical memory, additional configuration mechanisms need to be activated, or more recent processors needs to be exploited as we shall see

#### i386 memory layout at kernel startup for kernel 2.4

#### Actual issues to be tackled

- 1. We need to reach the correct granularity for paging (4KB rather than 4MB)

- 2. We need to span logical to physical address across the whole 1GB of kernel-manageable physical memory

- 3. We need to re-organize the page table in two separate levels

- 4. So we need to determine 'free buffers' within the already reachable memory segment to initially expand the page table

- 5. We cannot use memory management facilities other than paging (since core maps and free lists are not yet at steady state)

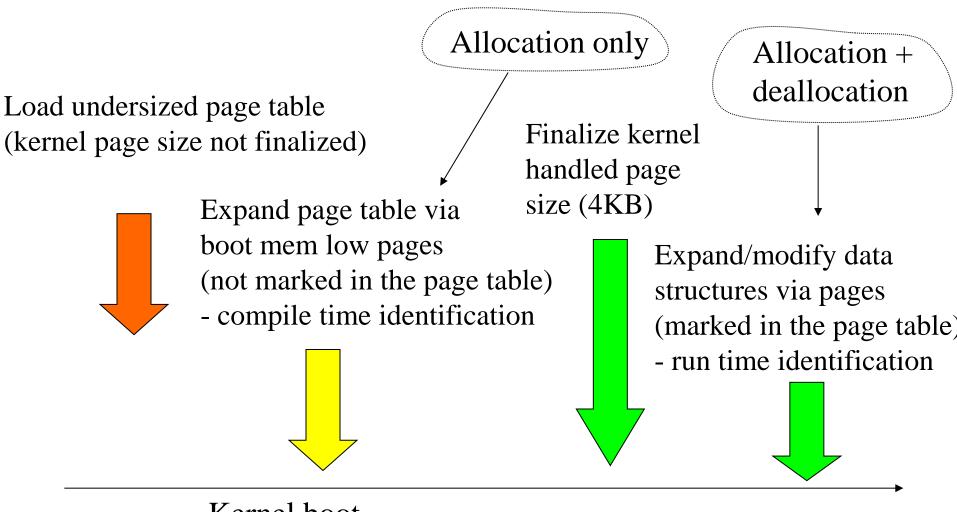

## Back to the concept of bootmem

- 1. Memory occupancy and location of the initial kernel image is determined by the compile/link process

- 2. A compile/link time memory manager is embedded into the kernel image, which is called bootmem manager

- 3. It relies on bitmaps telling if any 4KB page in the currently reachable memory image is busy or free

- 4. It also offers API (to be employed at boot time) in order to get free buffers

- 5. These buffers are sets of contiguous (or single) page aligned areas

- 6. As hinted, this subsystem is in charge of handling \_init marked functions in terms of final release of the corresponding buffers

## Kernel page table collocation within physical memory

## Low level "pages"

Load undersized page table (kernel page size not finalized: 4MB)

- 4 KB (1K entry)

Finalize kernel handled page size (4KB)

Expand page table via boot mem low pages (not marked in the page table)

- compile time identification

Kernel boot

#### LINUX paging vs i386

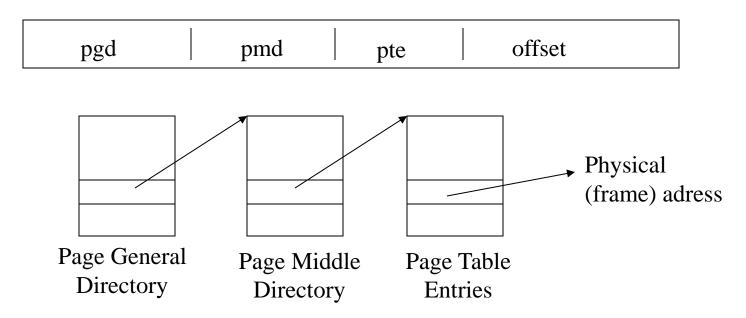

• LINUX virtual addresses exhibit (at least) 3 indirection levels

- On i386 machines, paging is supported limitedly to 2 levels (pde, page directory entry pte, page table entry)

- Such a dicotomy is solved by setting null the pmd field, which is proper of LINUX, and mapping

- ▶pgd LINUX on pde i386

- >pte LINUX on pte i386

#### i386 page table size

- Both levels entail 4 KB memory blocks

- Each block is an array of 4-byte entries

- Hence we can map 1 K x 1K pages

- Since each page is 4 KB in sixe, we get a 4 GB virtual addressing space

- The following macros define the size of the page tables blocks (they can be found in the file include/asm-i386/pgtable-2level.h)

```

▶#define PTRS_PER_PGD 1024

▶#define PTRS_PER_PMD 1

▶#define PTRS_PER_PTE 1024

```

• the value1 for PTRS\_PER\_PMD is used to simulate the existence of the intermediate level such in a way to keep the 3-level oriented software structure to be compliant with the 2-level architectural support

### Page table data structures

- A core structure is represented by the symbol swapper\_pg\_dir which is defined within the file arch/i386/kernel/head.S

- This symbol expresses the virtual memory address of the **PGD (PDE)** portion of the kernel page table

- This value is initialized at compile time, depending on the memory layout defined for the kernel bootable image

- Any entry within the PGD is accessed via displacement starting from the initial PGD address

- The C types for the definition of the content of the page table entries on i386 are defined in include/asm-i386/page.h

- They are

```

typedef struct { unsigned long pte_low; } pte_t;

typedef struct { unsigned long pmd; } pmd_t;

typedef struct { unsigned long pgd; } pgd_t;

```

### **Debugging**

- The redefinition of different structured types, which are identical in size and equal to an unsigned long, is done for debugging purposes

- Specifically, in C technology, <u>different aliases for the same type</u> are considered as identical types

- typedef unsigned long pgd\_t;

typedef unsigned long pte\_t;

• For instance, if we define

pgd t x; pte t y;

the compiler enables assignments such as x=y and y=x

• Hence, there is the need for defining different structured types which simulate the base types that would otherwise give rise to compiler equivalent aliases

#### i386 PDE entries

#### Page-Directory Entry (4-KByte Page Table)

| 31                                                                                               | 12 | 11  | 9   | 8 | 7  | 6 | 5 | 4   | 3           | 2           | 1           | 0 |

|--------------------------------------------------------------------------------------------------|----|-----|-----|---|----|---|---|-----|-------------|-------------|-------------|---|

| Page-Table Base Address                                                                          |    | Ava | ail | G | PS | 0 | Α | PCD | P<br>W<br>T | U<br>/<br>S | R<br>/<br>W | Р |

| Available for system programmer's use Global page (Ignored) ———————————————————————————————————— |    |     |     |   |    |   |   |     |             |             |             |   |

Nothing tells whether we can fetch (so execute) from there

#### i386 PTE entries

#### Page-Table Entry (4-KByte Page)

| 31                                             |                                                                                                                                               | 12 | 11   | 9 | 8 | 7           | 6 | 5 | 4   | 3           | 2           | 1           | 0 |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|----|------|---|---|-------------|---|---|-----|-------------|-------------|-------------|---|

|                                                | Page Base Address                                                                                                                             |    | Avai | I | G | P<br>A<br>T | D | Α | PCD | P<br>W<br>T | U<br>/<br>S | R<br>/<br>W | Р |

| Glo<br>Pa<br>Dir<br>Ac<br>Ca<br>Wr<br>Us<br>Re | railable for system programmer's use obal Page age Table Attribute Index rty cessed ache Disabled rite-Through ser/Supervisor ead/Write esent |    |      |   |   |             |   |   |     |             |             |             |   |

Nothing tells whether we can fetch (so execute) from there

#### **Field semantics**

- **Present**: indicates whether the page or the pointed page table is loaded in physical memory. This flag is not set by firmware (rather by the kernel)

- **Read/Write**: define the access privilege for a given page or a set of pages (as for PDE). Zero means read only access

- User/Supervisor: defines the privilege level for the page or for the group of pages (as for PDE). Zero means supervisor privilege

- Write Through: indicates the caching policy for the page or the set of pages (as for PDE). Zero means write-back, non-zero means write-through

- Cache Disabled: indicates whether caching is enabled or disabled for a page or a group of pages. Non-zero value means disabled caching (as for the case of memory mapped I/O)

- **Accessed**: indicates whether the page or the set of pages has been accessed. This is a sticky flag (no reset by firmware). Reset is controlled via software

- **Dirty**: indicates whether the page has been write-accessed. This is also a sticky flag

- Page Size (PDE only): if set indicates 4 MB paging otherwise 4 KB paging

- Page Table Attribute Index: ..... Do not care ......

- Page Global (PTE only): defines the caching policy for TLB entries.

Non-zero means that the corresponding TLB entry does not require reset upon loading a new value into the page table pointer CR3

### Bit masking

- in include/asm-i386/pgtable.h there exist some macros defining the positioning of control bits within the entries of the PDE or PTE

- There also exist the following macros for masking and setting those bits

• These are all machine dependent macros

#### An example

```

pte t x;

x = ...;

if ((x.pte low) & PAGE PRESENT) {

/* the page is loaded in a frame */

else{

/* the page is not loaded in any

frame */

```

### Relations with trap/interrupt events

- Upon a TLB miss, firmware accesses the page table

- The first checked bit is typically \_PAGE\_PRESENT

- If this bit is zero, a page fault occurs which gives rise to a trap (with a given displacement within the trap/interrupt table)

- Hence the instruction that gave rise to the trap can get finally re-executed

- Re-execution might give rise to additional traps, depending on firmware checks on the page table

- As an example, the attempt to access a read only page in write mode will give rise to a trap (which triggers the segmentation fault handler)

# Run time detection of current page size on IA-32 processors and 2.4 Linux kernel

#### Kernel page table initialization details

- As said, the kernel PDE is accessible at the virtual address kept by swapper\_pg\_dir (now init\_level4\_pgt on x86-64/kernel 3 or init top pgt on x86-64/kernel4)

- The room for PTE tables gets reserved within the 8MB of RAM that are accessible via the initial paging scheme

- Reserving takes place via the macro alloc\_bootmem\_low\_pages() which is defined in include/linux/bootmem.h (this macro returns a virtual address)

- Particularly, it returns the pointer to a 4KB (or 4KB x N) buffer which is page aligned

- This function belongs to the (already hinted) basic memory management subsystem upon which the LINUX memory system boot lies on

### Kernel 2.4/i386 initialization algorithm

- we start by the PGD entry which maps the address 3 GB, namely the entry numbered 768

- cyclically

- 1. We determine the virtual address to be memory mapped (this is kept within the vaddr variable)

- 2. One page for the PTE table gets allocated which is used for mapping 4 MB of virtual addresses

- 3. The table entries are populated

- 4. The virtual address to be mapped gets updated by adding 4 MB

- 5. We jump to step 1 unless no more virtual addresses or no more physical memory needs to be dealt with (the ending condition is recorded by the variable end)

### Initialization function pagetable init()

```

for (; i < PTRS PER PGD; pgd++, i++) {

vaddr = i*PGDIR SIZE; /* i is set to map from 3 GB */

if (end && (vaddr >= end)) break;

pmd = (pmd t *)pgd;/* pgd initialized to (swapper pg dir+i) */

for (j = 0; j < PTRS PER PMD; pmd++, j++) {

pte base = pte = (pte t *) alloc bootmem low pages(PAGE SIZE);

for (k = 0; k < PTRS PER PTE; pte++, k++) {

vaddr = i*PGDIR SIZE + j*PMD SIZE + k*PAGE SIZE;

if (end && (vaddr >= end)) break;

*pte = mk pte phys( pa(vaddr), PAGE KERNEL);

set pmd(pmd, pmd( KERNPG TABLE + pa(pte base)));

```

#### Note!!!

- The final PDE buffer coincides with the initial page table that maps 4 MB pages

- 4KB paging gets activated upon filling the entry of the PDE table (since the Page Size bit gets updated)

- For this reason the PDE entry is set only after having populated the corresponding PTE table to be pointed

- Otherwise memory mapping would be lost upon any TLB miss

### The set\_pmd macro

```

#define set pmd(pmdptr, pmdval) (*(pmdptr) = pmdval)

```

- Thia macro simply sets the value into one PMD entry

- Its input parameters are

- > the pmdptr pointer to an entry of PMD (the type is pmd t)

- The value to be loaded pmdval (of type pmd\_t, defined via casting)

- While setting up the kernel page table, this macro is used in combination with \_\_pa() (physical address) which returns an unsigned long

- The latter macro returns the physical address corresponding to a given virtual address within kernel space (except for some particular virtual address ranges, those non-directly mapped)

- Such a mapping deals with [3,4) GB virtual addressing onto [0,1) GB physical addressing

### The mk\_pte\_phys() macro

```

mk_pte_phys(physpage, pgprot)

```

- The input parameters are

- A frame physical address physpage, of type unsigned long

- > A bit string paprot for a PTE, of type paprot t

- The macro builds a complete PTE entry, which includes the physical address of the target frame

- The result type is pte\_t

- The result value can be then assigned to one PTE entry

## PAE (Physical address extension)

- increase of the bits used for physical addressing

- offered by more recent x86 processors (e.g. Intel Pentium Pro) which provide up to 36 bits for physical addressing

- we can drive up to 64 GB of RAM memory

- paging gets operated at 3 levels (instead of 2)

- the traditional page tables get modified by extending the entries at 64-bits and reducing their number by a half (hence we can support 1/4 of the address space)

- an additional top level table gets included called "page directory pointer table" which entails 4 entries, pointed by CR3

- CR4 indicates whether PAE mode is activated or not (which is done via bit 5 PAE-bit)

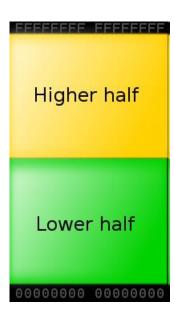

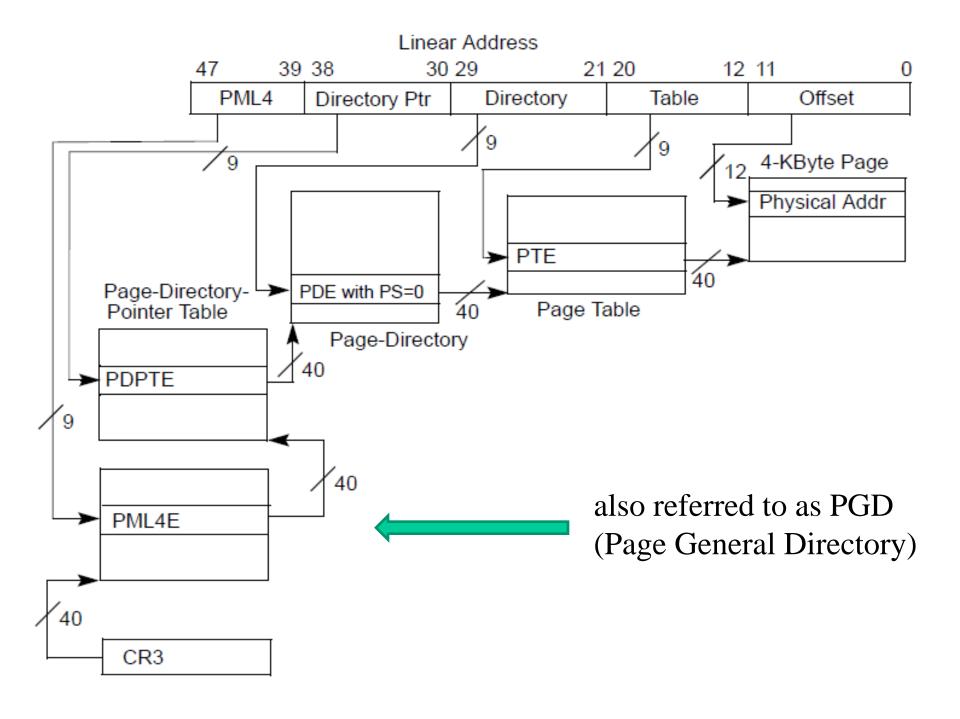

### x86-64 architectures

- They extend the PAE scheme via a so called "long addressing mode"

- Theoretically they allow addressing 2^64 bytes of logical memory

- In actual implementations we reach up to 2^48 canonical form addresses (lower/upper half within a total address space of 2^48)

- The total allows addressing to span over 256 TB

- Not all operating systems allow exploiting the whole range up to 256 TB of logical/physical memory

- LINUX currently allows for 128 TB for logical addressing of individual processes and 64 TB for physical addressing

### **Addressing scheme**

64-bit

48 out of 64-bit

### Linux address space on x86-64 processors

### 48-bit addressing: page tables

- Page directory pointer has been expanded from 4 to 512 entries

- An additional paging level has been added thus reaching 4 levels, this is called "Page-Map level"

- Each Page-Map level table has 512 entries

- Hence we get 512<sup>4</sup> pages of size 4 KB that are addressable (namely, a total of 256 TB)

| 6<br>3 | 6 6 6 5 5 5 5 5 5 5 5 5 5 2 1 0 9 8 7 6 5 4 3 2 | 5<br>1 M <sup>1</sup> | M-1 3 3 3 2 1 0              | 2 2 2 2 2 2 2 2 2 2<br>9 8 7 6 5 4 3 2 1     | 2 1 1 1 1 1 1 1 1<br>0 9 8 7 6 5 4 3 | 1 1 1<br>2 1 0 9 | 8 7        | 6 5           | 4           | 3 2 1                                                                                   | 0        |                             |  |  |  |                 |  |                   |

|--------|-------------------------------------------------|-----------------------|------------------------------|----------------------------------------------|--------------------------------------|------------------|------------|---------------|-------------|-----------------------------------------------------------------------------------------|----------|-----------------------------|--|--|--|-----------------|--|-------------------|

|        | Reserved <sup>2</sup>                           |                       |                              |                                              |                                      |                  |            |               |             | Address of PML4 table Ignored C                                                         |          |                             |  |  |  | P<br>W Ign<br>T |  | CR3               |

| 3<br>D | Ignored                                         | Rsvd.                 | Address                      | Address of page-directory-pointer table Ign. |                                      |                  |            |               |             | Address of page-directory-pointer table Ign. Rs   I   P   P   P   P   P   P   P   P   P |          |                             |  |  |  |                 |  | PML4E:<br>present |

|        |                                                 |                       |                              | Ignored                                      |                                      | •                | •          |               |             |                                                                                         | <u>0</u> | PML4E:<br>not<br>present    |  |  |  |                 |  |                   |

| X<br>D | Ignored                                         | Rsvd.                 | Address of<br>1GB page frame | Reser                                        | ved                                  | P<br>A Ign.<br>T | G <u>1</u> |               |             | P U R<br>W/S W                                                                          |          | PDPTE:<br>1GB<br>page       |  |  |  |                 |  |                   |

| X<br>D | Ignored                                         | Rsvd.                 | F                            | Address of page directory                    |                                      |                  |            | I<br>g A<br>n | D<br>P      | P U R<br>W/S W                                                                          | 1        | PDPTE:<br>page<br>directory |  |  |  |                 |  |                   |

|        |                                                 |                       | •                            | Ignored                                      |                                      | •                | ·          |               |             |                                                                                         | <u>0</u> | PDTPE:<br>not<br>present    |  |  |  |                 |  |                   |

| X<br>D | Ignored                                         | Rsvd.                 |                              | dress of<br>age frame                        | Reserved                             | P<br>A Ign.<br>T | G <u>1</u> |               | - 1 - 1     | P U R<br>W/S /<br>T                                                                     |          | PDE:<br>2MB<br>page         |  |  |  |                 |  |                   |

| X<br>D | Ignored                                         | Rsvd.                 |                              | Address of page tal                          | ble                                  | lgn.             | 0          | I<br>g A<br>n | P<br>C<br>D | P U R<br>W/S W                                                                          | 1        | PDE:<br>page<br>table       |  |  |  |                 |  |                   |

|        |                                                 |                       |                              | Ignored                                      |                                      |                  |            |               |             |                                                                                         | <u>0</u> | PDE:<br>not<br>present      |  |  |  |                 |  |                   |

| X<br>D | Ignored                                         | Rsvd.                 | A                            | ddress of 4KB page t                         | frame                                | lgn.             | G A<br>T   | D A           | P<br>C<br>D | P U R<br>W /S W                                                                         | 1        | PTE:<br>4KB<br>page         |  |  |  |                 |  |                   |

|        |                                                 |                       |                              | Ignored                                      |                                      |                  |            |               | -           |                                                                                         | <u>0</u> | PTE:<br>not<br>present      |  |  |  |                 |  |                   |

Figure 4-11. Formats of CR3 and Paging-Structure Entries with IA-32e Paging

Table 4-19. Format of an IA-32e Page-Table Entry that Maps a 4-KByte Page

| Bit<br>Position(s) | Contents                                                                                                                                                                           |

|--------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 (P)              | Present; must be 1 to map a 4-KByte page                                                                                                                                           |

| 1 (R/W)            | Read/write; if 0, writes may not be allowed to the 4-KByte page referenced by this entry (see Section 4.6)                                                                         |

| 2 (U/S)            | User/supervisor; if 0, user-mode accesses are not allowed to the 4-KByte page referenced by this entry (see Section 4.6)                                                           |

| 3 (PWT)            | Page-level write-through; indirectly determines the memory type used to access the 4-KByte page referenced by this entry (see Section 4.9.2)                                       |

| 4 (PCD)            | Page-level cache disable; indirectly determines the memory type used to access the 4-KByte page referenced by this entry (see Section 4.9.2)                                       |

| 5 (A)              | Accessed; indicates whether software has accessed the 4-KByte page referenced by this entry (see Section 4.8)                                                                      |

| 6 (D)              | Dirty; indicates whether software has written to the 4-KByte page referenced by this entry (see Section 4.8)                                                                       |

| 7 (PAT)            | Indirectly determines the memory type used to access the 4-KByte page referenced by this entry (see Section 4.9.2)                                                                 |

| 8 (G)              | Global; if CR4.PGE = 1, determines whether the translation is global (see Section 4.10); ignored otherwise                                                                         |

| 11:9               | Ignored                                                                                                                                                                            |

| (M-1):12           | Physical address of the 4-KByte page referenced by this entry                                                                                                                      |

| 51:M               | Reserved (must be 0)                                                                                                                                                               |

| 62:52              | Ignored                                                                                                                                                                            |

| 63 (XD)            | If IA32_EFER.NXE = 1, execute-disable (if 1, instruction fetches are not allowed from the 4-KByte page controlled by this entry; see Section 4.6); otherwise, reserved (must be 0) |

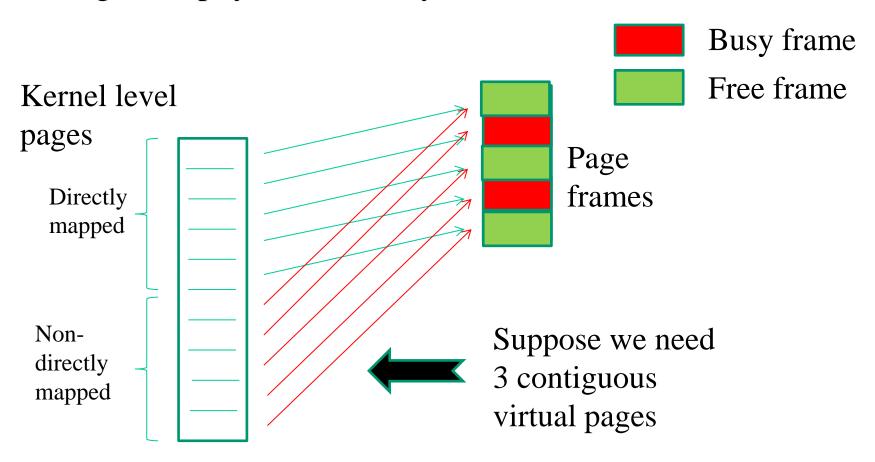

### Direct vs non-direct page mapping

- In long mode x86 processors allow one entry of the PML4 to be associated with 2^27 frames

- This amounts to  $2^29 \text{ KB} = 2^9 \text{ GB} = 512 \text{ GB}$

- Clearly, we have plenty of room in virtual addressing for directly mapping all the available RAM into kernel pages on most common chipsets

- This is the typical approach taken by Linux, where we directly map all the RAM memory

- However we also remap the same RAM memory in nondirect manner whenever required

### Huge pages

- Ideally x86-64 processors support them starting from PDPT

- Linux typically offers the support for huge pages pointed to by the PDE (page size 512\*4KB)

- See: /proc/meminfo and /proc/sys/vm/nr\_hugepages

- These can be "mmaped" via file descriptors and/or mmap parameters (e.g. MAP\_HUGETLB flag)

- They can also be requested via the madvise (void\*, size\_t, int) system call (with MADV\_HUGEPAGE flag)

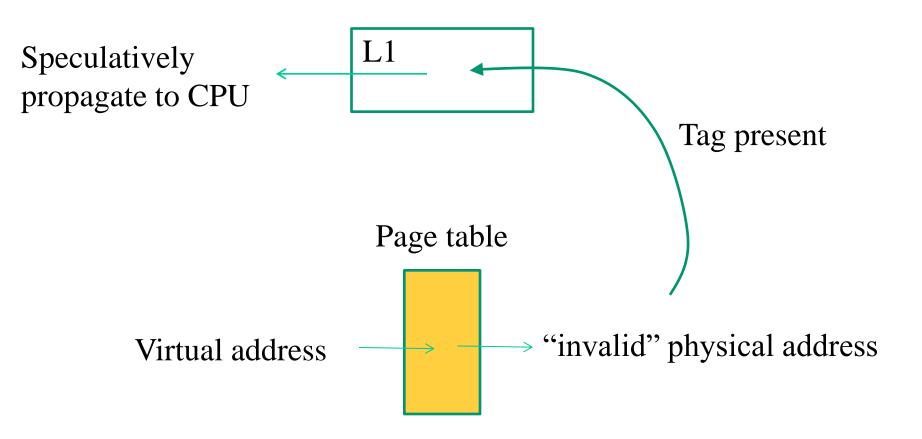

### Back to speculation in the hardware

- From Meldown we already know that a page table entry plays a central role in hardware side effects with speculative execution

- The page table entry provides the physical address of some "non-accessible" byte, which is still accessible in speculative mode

- This byte can flow into speculative incarnations of registers and can be used for cache side effects

- ..... but, what about a page table entry with "presence bit" not set???

- ..... is there any speculative action that is still performed by the hardware with the content of that page table entry?

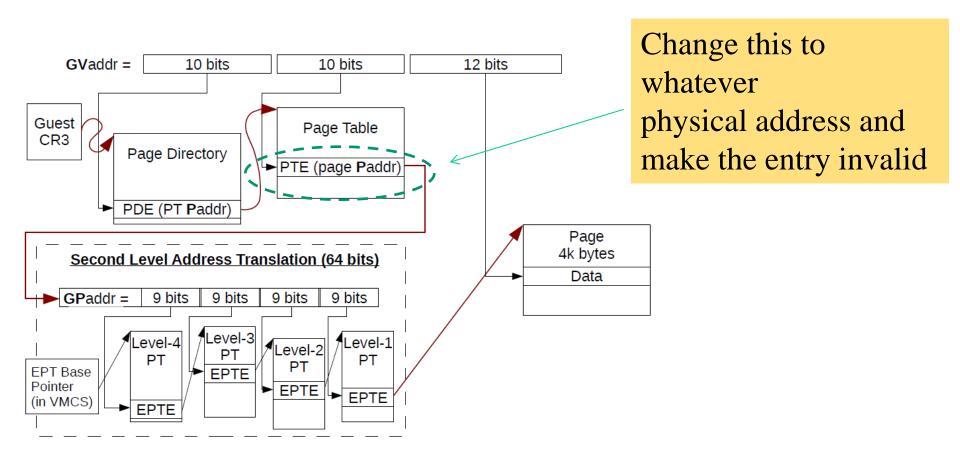

### The L1 Terminal Fault (L1TF) attack

- It is based on the exploitation of data cached into L1

- More in detail:

- A page table entry with presence bit set to 0 propagates the value of the target physical memory location (the TAG) upon loads if that memory location is already cached into L1

- ➤ If we use the value of that memory location as an index (Meltdown style) we can grub it via side effects on cache latency

- Overall, we can be able to indirectly read the content of any physical memory location if the same location has already been read, e.g., in the context of another process on the same CPU-core

- Affected CPUs: AMD, Intel ATOM, Intel Xeon PHI ...

### The scheme

### L1TF big issues

- To exploit L1TF we must drive page table entries

- A kernel typically does not allow it (in fact kernel mitigation of this attack simply relies on having "invalid" page table entries set to proper values not mapping cacheable data)

- But what about a guest kernel?

- It can attack physical memory of the underlying host

- So it can also attack memory of co-located guests/VMs

- It is as simple as hacking the guest level page tables, on which an attacker that drives the guest may have full control

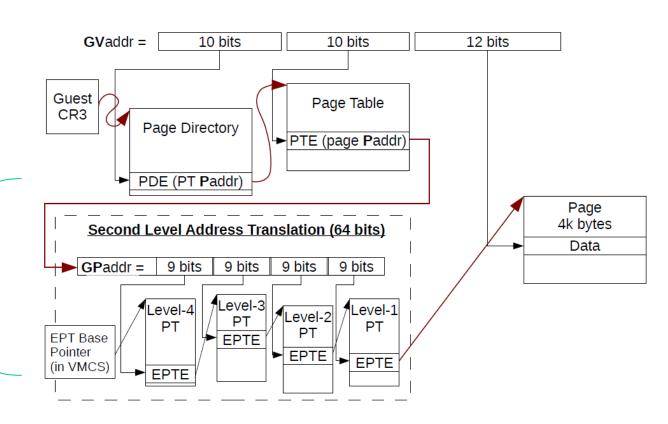

# Hardware supported "virtual memory" virtualization

- Intel Extended Page Tables (EPT)

- AMD Nested Page Tables (NPT)

- A scheme:

Keeps track of the physical memory location of the page frames used for activated VM

## Attacking the host physical memory

### Reaching vs allocating/deallocating memory

Kernel boot

### Core map

- It is an array of mem\_map\_t (also known as struct page) structures defined in include/linux/mm.h

- The actual type definition is as follows (or similar along kernel advancement):

```

typedef struct page {

/* ->mapping has some page lists. */

struct list head list;

/* The inode (or ...) we belong to. */

struct address space *mapping;

unsigned long index;

/* Our offset within mapping. */

/* Next page sharing our hash bucket in

struct page *next hash;

the pagecache hash table. */

/* Usage count, see below. */

atomic t count;

unsigned long flags;

/* atomic flags, some possibly

updated asynchronously */

/* Pageout list, eq. active list;

struct list head lru;

protected by pagemap lru lock !! */

struct page **pprev hash; /* Complement to *next hash. */

struct buffer head * buffers; /* Buffer maps us to a disk block. */

#if defined(CONFIG HIGHMEM) || defined(WANT PAGE VIRTUAL)

void *virtual;

/* Kernel virtual address (NULL if

not kmapped, ie. highmem) */

#endif /* CONFIG HIGMEM || WANT PAGE VIRTUAL */

} mem map t;

```

#### **Fields**

- Most of the fields are used to keep track of the interactions between memory management and other kernel sub-systems (such as I/O)

- Memory management proper fields are

- > struct list\_head list (whose type is defined in include/linux/lvm.h), which is used to organize the frames into free lists

- ➤ atomic\_t count, which counts the virtual references mapped onto the frame (it is managed via atomic updates, such as with LOCK directives)

- > unsigned long flags, this field keeps the status bits for the frame, such as:

```

#define PG_locked 0

#define PG_referenced 2

#define PG_uptodate 3

#define PG_dirty 4

#define PG_lru 6

#define PG_lru 6

```

## Core map initialization (i386/kernel 2.4 example)

- Initially we only have the core map pointer

- This is mem\_map and is declared in mm/memory.c

- Pointer initialization and corresponding memory allocation occur within free area init()

- After initializing, each entry will keep the value 0 within the count field and the value 1 into the PG\_reserved flag within the flags field

- Hence no virtual reference exists for that frame and the frame is reserved

- Frame un-reserving will take place later via the function mem\_init() in arch/i386/mm/init.c (by resetting the bit PG reserved)

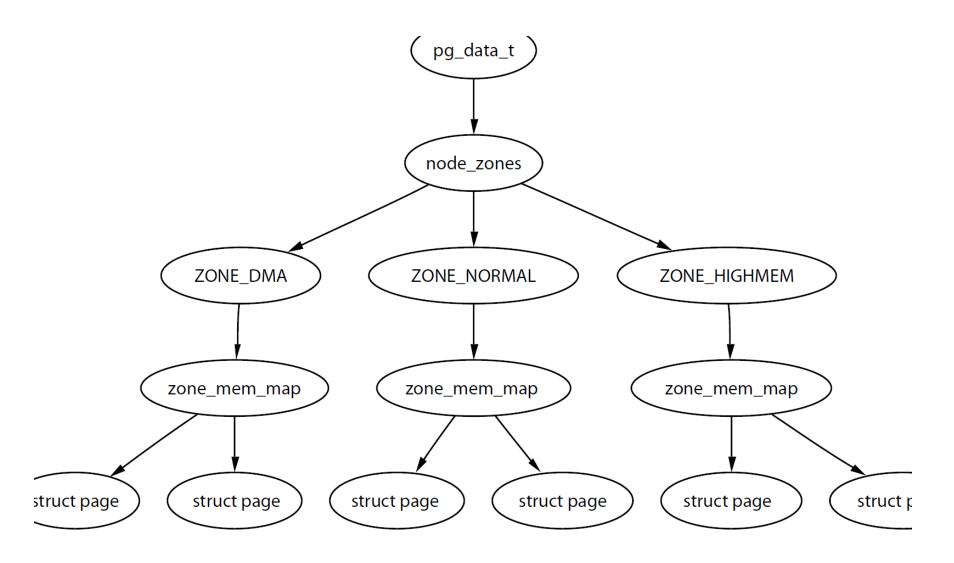

# Free list organization: single NUMA zone – or NUMA unaware – protected mode case (e.g. kernel 2.4)

- we have 3 free lists of frames, depending on the frame positioning within the following zones: DMA (DMA ISA operations), NORMAL (room where the kernel can reside), HIGHMEM (room for user data)

- The corresponding defines are in include/linux/mmzone.h:

```

#define ZONE_DMA 0

#define ZONE_NORMAL 1

#define ZONE_HIGHMEM 2

#define MAX NR ZONES 3

```

• The corresponding sizes are usually defined as

#### Free list data structures

• Free lists information is kept within the pg\_data\_t data structure defined in include/linux/mmzone.h, and whose actual instance is contig\_page\_data, which is declared in mm/numa.c

```

typedef struct pglist data {

zone t node zones[MAX NR ZONES];

zonelist t node zonelists[GFP ZONEMASK+1];

int nr zones;

Field of

struct page *node mem map;

unsigned long *valid addr bitmap;

interest

struct bootmem data *bdata;

unsigned long node start paddr;

unsigned long node start mapnr;

unsigned long node size;

int node id;

struct pglist data *node next;

pg data t;

```

• the zone\_t type is defined in include/linux/mmzone.h as follows

```

Beware this!

typedef struct zone struct {

spinlock t

lock;

unsigned -----long free pages;

zone watermarks t watermarks [MAX NR ZONES];

unsigned long

need balance;

unsigned long nr active pages, nr_inactive_pages;

unsigned long

nr cache pages;

free area t

free area[MAX ORDER];

* wait table;

wait queue head t

unsigned long

wait table size;

unsigned long

wait table shift;

Up to 11 in

Fields of

struct pglist data

*zone pgdat;

recent

interest

*zone_mem_map;

struct page

kernel versions

unsigned long

zone start paddr;

(it was typically

unsigned long

zone start mapnr;

5 before)

char

*name;

unsigned long

size;

unsigned long

realsize;

zone t;

```

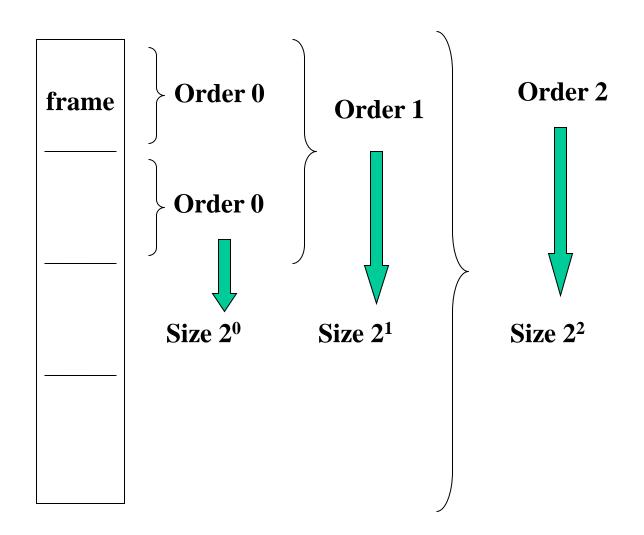

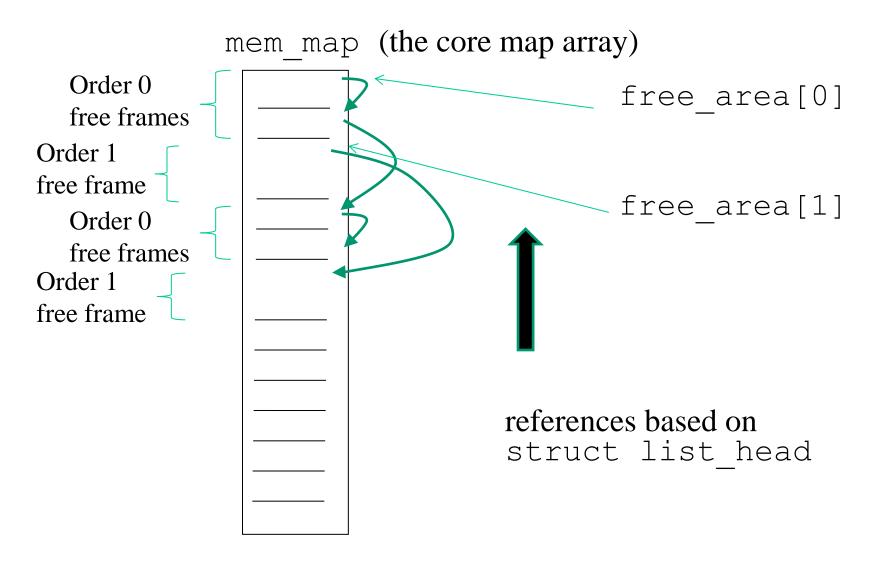

## **Buddy system features**

• free area t is defined in the same file as

where

```

struct list_head {

struct list_head *next, *prev;

}

```

- overall, any element of the free\_area[] array keeps

- A pointer to the first free frame associated with blocks of a given order

- A pointer to a bitmap that keeps fragmentation information according to the 'buddy system' organization

## Buddy allocation vs core map vs free list

Recall that spinlocks are used to manage this data structure

# A scheme (picture from: Understanding the Linux Virtual Memory Manager – Mel Gorman)

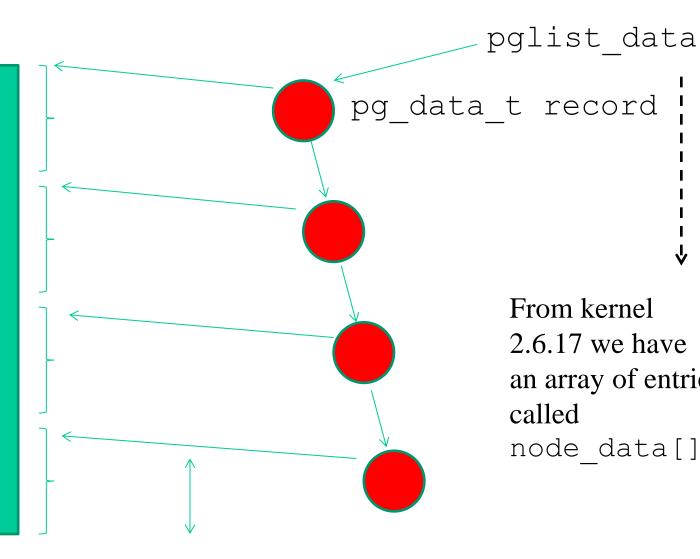

## Jumping to more recent kernels for NUMA machines – kernel 2.6

- The concept of multiple NUMA zones is represented by a struct pglist\_data even if the architecture is Uniform Memory Access (UMA)

- This struct is always referenced by its typedef pg\_data\_t

- Every node in the system is kept on a NULL terminated list called pgdat\_list, and each node is linked to the next with the field pg data t-node next

- For UMA architectures like PC desktops, only one static pg\_data\_t structure, as already seen, called contig\_page\_data is used

mem map

## A scheme

One buddy allocator per each node

From kernel 2.6.17 we have an array of entries called node data[]

struct page \*node mem map

## Summarizing (still for the 2.4 kernel example)

- Architecture setup occurs via setup\_arch() which will give rise to

- ➤ a Core Map with all reseved frames

- Free lists that looks like if no frame is available (in fact they are all reserved at this stage)

- Most of the work is done by free\_area\_init()

- This relies on bitmaps allocation services based on alloc\_bootmem()

### Releasing boot used pages to the free lists

```

static unsigned long init

free all bootmem core(pg data t *pgdat)

for (i = 0; i < idx; i++, page++) {

if (!test bit(i, bdata->node bootmem map)) {

// il frame non deve restare riservato

count++;

ClearPageReserved(page);

set page count (page, 1);

free page(page);

total += count;

return total;

```

# Allocation contexts (more generally, kernel level execution contexts)

#### Process context

- Allocation is caused by a system call

- Not satisfiable → wait is experienced along the current execution trace

- Priority based schemes

#### • Interrupt

- Allocation requested by an interrupt handler

- Not satisfiable → no-wait is experienced along the current execution trace

- Priority independent schemes

#### **Buddy-system API**

- After booting, the memory management system can be accessed via proper APIs, which drive operations on the aforementioned data structures

- The prototypes are in #include linux/malloc.h>

- The very base allocation APIs are (bare minimal page aligned allocation)

- unsigned long get\_zeroed\_page(int flags)

removes a frame from the free list, sets the content to zero and returns

the virtual address

- unsigned long \_\_get\_free\_page(int flags)

removes a frame from the free list and returns the virtual address

- unsigned long \_\_get\_free\_pages(int flags, unsigned long order)

- removes a block of contiguous frames with given order from the free list and returns the virtual address of the first frame

- void free\_page (unsigned long addr)

puts a frame into the free list again, having a given initial virtual

address

- void free\_pages (unsigned long addr,

unsigned long order)

puts a block of frames of given order into the free list again

Note!!!!!!! Wrong order gives rise to kernel corruption in

several kernel configurations

#### flags: used contexts

GFP\_ATOMIC the call cannot lead to sleep (this is for interrupt contexts)

GFP\_USER - GFP\_BUFFER - GFP\_KERNEL the call can lead to sleep

## **Buddy allocation vs direct mapping**

- All the buddy-system API functions return virtual addresses of direct mapped pages

- We can therefore directly discover the position in memory of the corresponding frames

- Also, memory contiguousness is guaranteed for both virtual and physical addresses

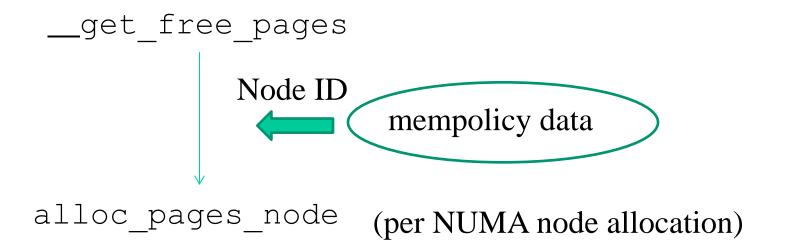

#### Binding actual allocation to NUMA nodes

The real core of the Linux page allocator is the function

```

struct page *alloc_pages_node(int nid, unsigned

int flags, unsigned int order);

```

Hence the actual allocation chain is:

#### Mem-policy details

- Generally speaking, mem-policies determine what NUMA node needs to be involved in a specific allocation operation which is thread specific

- Starting from kernel 2.6.18, the determination of mem-policies can be configured by the application code via system calls

#### **Synopsis**

```

#include <numaif.h>

int set_mempolicy(int mode, unsigned long

*nodemask, unsigned long maxnode);

```

sets the NUMA memory policy of the calling process, which consists of a policy mode and zero or more nodes, to the values specified by the *mode*, *nodemask* and *maxnode* arguments

The *mode* argument must specify one of MPOL\_DEFAULT, MPOL\_BIND, MPOL\_INTERLEAVE or MPOL\_PREFERRED

#### ... another example

#### **Synopsis**

```

#include <numaif.h>

int mbind(void *addr, unsigned long len, int

mode, unsigned long *nodemask, unsigned long

maxnode, unsigned flags);

```

sets the NUMA memory policy, which consists of a policy mode and zero or more nodes, for the memory range starting with *addr* and continuing for *len* bytes. The memory policy defines from which node memory is allocated.

#### ... finally you can also move pages around

#### **Synopsis**

```

#include <numaif.h>

long move_pages(int pid, unsigned long count,

void **pages, const int *nodes, int *status,

int flags);

```

moves the specified *pages* of the process *pid* to the memory nodes specified by *nodes*. The result of the move is reflected in *status*. The *flags* indicate constraints on the pages to be moved.

# The case of frequent allocation/deallocation of a target-specific data structures

- Here we are talking about allocation/deallocation operations of data structures

- 1. that are used for a target-specific objective (e.g. in terms of data structures to be hosted)

- 2. which are requested/released frequently

- The problem is that getting the actual buffers (pages) from the buddy system will lead to contention and consequent synchronization costs (does not scale)

- In fact the (per NUMA node) buddy system operates with spinlock synchronized critical sections

- Kernel design copes with this issue by using pre-reserved buffers with lightweight allocation/release logic

#### ... a classical example

- The allocation and deletion of page tables, at any level, is a very frequent operation, so it is important the operation is as quick as possible

- Hence the pages used for the page tables are cached in a number of different lists called *quicklists*

- For 3 levels paging, PGDs, PMDs and PTEs have two sets of functions each for the allocation and freeing of page tables.

- The allocation functions are pgd\_alloc(), pmd\_alloc() and pte\_alloc(), respectively the free functions are, predictably enough, called pgd\_free(), pmd\_free() and pte\_free()

- Broadly speaking, these APIs implement caching

#### **Actual quicklists**

- Defined in include/linux/quicklist.h

- They are implemented as a list of per-core page lists

- There is no need for synchronization

- If allocation fails, they revert to

```

__get_free_page()

```

### **Quicklist API and algorithm**

```

static inline void *quicklist alloc(int nr, gfp t flags, ...) {

struct quicklist *q;

void **p = NULL;

q = &get cpu var(quicklist)[nr];

p = q->page;

if (likely(p)) {

Beware these!!

q->page = p[0];

p[0] = NULL;

q->nr pages--;

put cpu var(quicklist);

if (likely(p))

return p;

p = (void *) get free page(flags | GFP ZERO);

return p;

```

# Logical/Physical address translation for kernel directly mapped memory

#### We can exploit the below macros

In generic kernel versions

#### SLAB (or SLUB) allocator: a cache of 'small' size buffers

- The prototypes are in #include ux/malloc.h>

- The main APIs are

- void (\*kmalloc(size\_t size, int flags)

allocation of contiguous memory of a given size it returns the virtual address

- void kfree(void \*obj)

frees memory allocated via kmalloc()

kzalloc() for

zeroed buffers

- Main features:

- ➤ Cache aligned delivery of memory chunks (performance optimal access of related data within the same chunk)

- ➤ Fast allocation/deallocation support

- Clearly, we can also perform node-specific requests via

## What about (very) large size allocations

- Classically employed while adding large size data structures to the kernel in a stable way

- We can go beyond the size-limit of the specific buy system implementation

- This is the case when, e.g., mounting external modules

- This time we are not guaranteed to get direct mapped pages

- The main APIs are:

- ➤ void \* vmalloc(unsigned long size);

allocates memory of a given size, which can be non-contiguous, and

returns the virtual address (the corresponding frames are anyhow

reserved)

- ➤ void vfree (void \* addr)

frees the above mentioned memory

#### kmalloc vs vmalloc: an overall reference picture

- Allocation size:

- > 128 KB for kmalloc (cache aligned)

- $\triangleright$  64/128 MB for vmalloc

- Physical contiguousness

- > Yes for kmalloc

- > No for vmalloc

- Effects on TLB

- > None for kmalloc

- ➤ Global for vmalloc (transparent to vmalloc users)

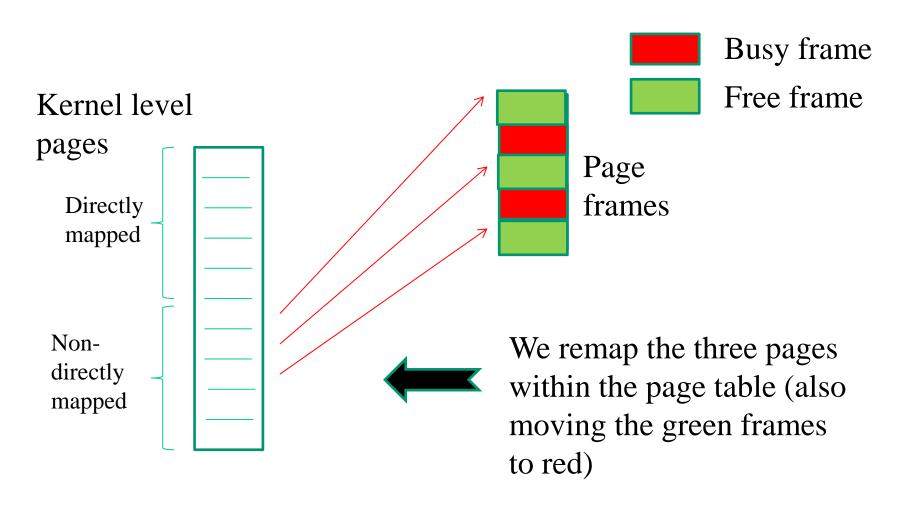

#### vmalloc operations (i)

• Based in remapping a range of contiguous pages in (non contiguous) physical memory

#### vmalloc operations (ii)

Clearly with vmalloc we typically remap much larger blocks of pages

#### Kernel-page remapping vs hardware state

- Kernel-page mapping has a "global nature"

- Any core can use the same mapping, supported by the same page tables

- When running vmalloc/vfree services on a specific core, all the other cores need to observe the update mapping

- Cached mappings within TLBs need therefore to be updated via proper operations

## TLB implicit vs explicit operations

- The level of automation in the management process of TLB entries depends on the specific hardware architecture

- Kernel hooks have to exist for explicit management of TLB operations (these are compile-time mapped to null operations in case of fully automated TLB management)

- For x86 processors automation is only partial

- Specifically, automatic TLB flushes occur upon updates of the CR3 register (e.g. page table changes)

- Changes inside the current page table are not automatically reflected within the TLB

## Types of TLB relevant events

- Scale classification

- ✓ Global: dealing with virtual addresses accessible by every CPU/core in real-time-concurrency

- ✓ Local: dealing with virtual addresses accessible in timesharing concurrency

- Typology classification

- ✓ Virtual to physical address remapping

- ✓ Virtual address access rule modification (read only vs write access)

- Typical management, TLB implicit renewal via flush operations

#### **TLB flush costs**

#### Direct costs

- ✓ The latency of the firmware level protocol for TLB entries invalidation (selective vs non-selective)

- ✓ **plus**, the latency for cross-CPU coordination in case of global TLB flushes

#### Indirect costs

- ✓ TLB renewal latency by the MMU firmware upon misses in the translation process of virtual to physical addresses

- ✓ This cost depends on the amount of entries to be refilled

- ✓ Tradeoff vs TLB API and software complexity inside the kernel (selective vs non-selective flush/renewal)

## LINUX global TLB flush

void flush tlb all (void)

- This flushes the entire TLB <u>on all processors</u> <u>running in the system</u>, which makes it the most expensive TLB flush operation

- After it completes, all modifications to the page tables will be visible globally

- This is required after the kernel page tables, which are global in nature, have been modified

- Examples are vmalloc()/vfree() operations

## LINUX global TLB flush vs x86

- x86 does not offer pure hardware support for flushing all the TLBs on board of the architecture

- It offers a baseline mechanism to let CPU-cores coordinate

- A softwar layer is used to drive what to do while coordinating (namely TLB invalidation)

- We will come back to this issue when analyzing actual interrupt achitectures on multi-core machines

#### The x86 timeline of vmalloc

#### **Invocation (on some generic CPU-core)**

return

- Acquire memory from the buddy allocator

- Update kernel page table

## LINUX partial TLB flush

void flush tlb mm(struct mm struct \*mm)

- This flushes all TLB entries related to the userspace portion for the requested mm context

- In some architectures (e.g. MIPS), this will need to be performed for all processors, but usually it is confined to the local processor

- This is only called when an operation has been performed that affects the entire address space

- e.g., after all the address mapping has been duplicated with dup\_mmap() for fork or after all memory mappings have been deleted with exit mmap()

- Interaction with COW protection

```

void flush_tlb_range(struct

mm_struct *mm, unsigned long

start, unsigned long end)

```

- This flushes all entries within the requested user space range for the mm context

- This is used after a region has been moved (e.g. mremap()) or when changing permissions (e.g. mprotect())

- This API is provided for architectures that can remove ranges of TLB entries quickly rather than iterating with flush tlb page()

```

void flush_tlb_page(struct

vm_area_struct *vma, unsigned long

addr)

```

- This API is responsible for flushing a single page from the TLB

- The two most common uses of it are for flushing the TLB after a page has been faulted in or has been paged out

- ✓ Interactions with page table access firmware

## x86 partial TLB invalidation

#### **INVLPG**

#### **Invalidate TLB Entry**

| Opcode  | Mnemonic | Description                                    |

|---------|----------|------------------------------------------------|

| 0F 01/7 | INVLPG m | Invalidate TLB Entry for page that contains m. |

#### Description

Invalidates (flushes) the translation lookaside buffer (TLB) entry specified with the source operand. The source operand is a memory address. The processor determines the page that contains that address and flushes the TLB entry for that page.

The INVLPG instruction is a privileged instruction. When the processor is running in protected mode, the CPL of a program or procedure must be 0 to execute this instruction.

The INVLPG instruction normally flushes the TLB entry only for the specified page; however, in some cases, it flushes the entire TLB. See "MOV-Move to/from Control Registers" in this chapter for further information on operations that flush the TLB.

#### Operation

Flush(RelevantTLBEntries);

ContinueExecution();

#### Flags affected

None.

#### IA-32 Architecture Compatibility

The INVLPG instruction is implementation dependent, and its function may be implemented differently on different families of IA-32 processors. This instruction is not supported on IA-32 processors earlier than the Intel486 processor.

void flush\_tlb\_pgtables(struct

mm\_struct \*mm, unsigned long start,

unsigned long end)

- This API is called when the page tables are being torn down and freed

- Some platforms cache the lowest level of the page table, i.e., the actual page frame storing entries, which needs to be flushed when the pages are being deleted (e.g. Sparc64)

- This is called when a region is being unmapped and the page directory entries are being reclaimed

```

void update_mmu_cache(struct

vm_area_struct *vma, unsigned long

addr, pte t pte)

```

- This API is only called after a page fault completes

- ➤ It tells that a new translation now exists at pte for the virtual address addr

- Each architecture decides how this information should be used

- In some cases it is used for <u>preloading TLB entries (e.g.</u> <u>like in ARM Cortex processors)</u>